PUBLIC

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev: 3.0-pre Date: 2022-04-12

Version 3.0-pre, 2022-04-12

# **Table of Contents**

| 1. Overview                                          | 4  |

|------------------------------------------------------|----|

| 2. Documentation Overview                            | 5  |

| 2.1. Target Manuals                                  | 5  |

| 2.2. Model Manuals                                   | 5  |

| 3. System Requirements                               | 7  |

| 3.1. Linux                                           | 7  |

| 4. Getting Started                                   | 8  |

| 4.1. Installation                                    | 8  |

| 4.2. License Files                                   | 9  |

| 4.3. Running the Emulator                            | 10 |

| 4.4. Creating a New Machine                          | 10 |

| 4.5. Loading and Running Software                    |    |

| 5. Support and Maintenance                           |    |

| 6. Command Line                                      | 13 |

| 6.1. Command Line Interface Options                  | 13 |

| 6.2. Command Syntax                                  | 14 |

| 6.3. Variables                                       | 14 |

| 6.4. Help Command                                    | 14 |

| 6.5. Commands                                        | 14 |

| 7. Libraries                                         |    |

| 7.1. Deprecation Policy                              |    |

| 7.2. Experimental Application Programming Interfaces | 19 |

| 8. Object System                                     | 20 |

| 8.1. Object Graph and Interface Properties           | 21 |

| 8.2. Object System Functions                         |    |

| 8.3. Properties                                      | 23 |

| 8.4. Pseudo Properties                               | 23 |

| 8.5. Interfaces                                      | 23 |

| 8.6. Ports.                                          | 23 |

| 9. Events                                            | 25 |

| 9.1. Events from Other Threads                       | 26 |

| 9.2. Notifications                                   | 26 |

| 10. Processor Emulation                              | 28 |

| 10.1. Running a CPU or Machine                       | 28 |

| 10.2. Event System                                   | 30 |

| 10.3. Multi-Core Emulation and Events                | 30 |

| 10.4. CPU Interface                                  |    |

#### PUBLIC

TEMU: User Manual

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

| 11. Memory Emulation                          | 33 |

|-----------------------------------------------|----|

| 11.1. Memory Spaces                           | 33 |

| 11.2. Memory Transactions                     | 33 |

| 11.3. Address Translation Cache               | 36 |

| 11.4. Memory Hierarchy and Caches             | 36 |

| 11.5. Interfaces                              | 38 |

| 12. Components.                               | 40 |

| 13. Snapshots                                 | 41 |

| 13.1. Snapshot Restore Phases                 | 41 |

| 13.2. JSON Caveats                            | 41 |

| 14. Software Debugging                        | 43 |

| 14.1. CLI Based Software Debugging            | 43 |

| 14.2. GDB Server.                             | 45 |

| 15. Profiling and Coverage                    | 48 |

| 15.1. Enabling Profiling Mode                 | 48 |

| 15.2. Exporting Profiles.                     | 48 |

| 16. Scripting                                 | 50 |

| 17. Examples                                  | 51 |

| 17.1. Quick CPU Construction Using JSON Files | 51 |

| 17.2. Command Line CPU Construction           | 51 |

| 17.3. Programmatic CPU Construction           | 52 |

| 18. Modelling Guide                           | 56 |

| 18.1. Introduction                            | 56 |

| 18.2. Basic.                                  | 56 |

| 18.3. Advanced                                | 66 |

| 18.4. Examples                                | 70 |

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

# **Chapter 1. Overview**

This document is the TEMU (Terma Emulator) Software Users Manual. It describes the fundamental concepts and general usage of the TEMU libraries and command line interface.

TEMU is a multi-achietecture microprocessor emulator. It currently supports the ARMv7, SPARCv8 and PowerPC instruction sets. Currently this includes: ERC32, LEON2, LEON3, LEON4, Cortex-R4/5 and PPC750. The emulator can emulate multi-core processors.

TEMU is a full system emulator. It is capable of emulating (multi-core) microprocessors, memory and peripherals. Different devices are written as plugins. Including CPUs, memory and device modules. In-fact, systems are constructed by connecting different modules together. Thus, there is no hard-wiring of devices to any particular memory layout.

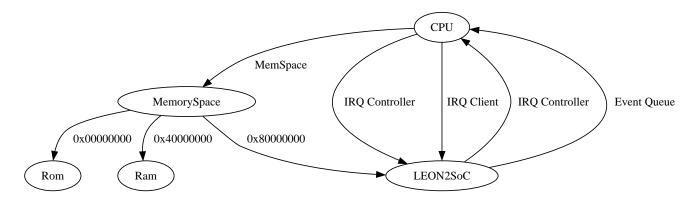

To give an example, in order to construct a LEON2 processor, one would first create and connect the CPU core, ROM, RAM and LEON2 SoC components.

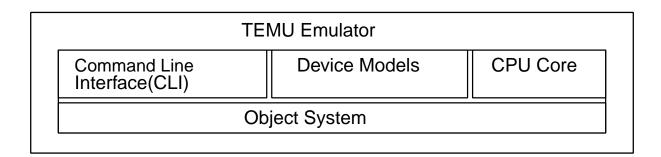

Figure 1. Layers of the Terma Emulator

There are two user interfaces for TEMU, the *Command Line Interface (CLI)* and the libraries (API). The CLI offers an interactive tool for running the emulator by itself. While the API allows the user to integrate the emulator with other simulators.

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

# **Chapter 2. Documentation Overview**

This document is the software users manual. It gives a high level overview of the system. However, as TEMU is modular, this manual does not document everything. The details are described in different target, model and API manuals. The target and model manuals are *reference documents*, and describe the properties and interfaces implemented by the relevant model.

# 2.1. Target Manuals

Target manuals describe the usage of the processor emulators. There is one target guide per supported architecture (currently this include only the SPARCv8). Note that a CPU core does not contain any I/O models.

Table 1. TEMU Target Manuals

| Document              | Description                          |

|-----------------------|--------------------------------------|

| ARMv7 Target Manual   | Manual for all the ARMv7 CPU cores   |

| SPARCv8 Target Manual | Manual for all the SPARC CPU cores   |

| PowerPC Target Manual | Manual for all the PowerPC CPU cores |

## 2.2. Model Manuals

Each implemented I/O model has a manual describing the usage of the model. That includes how to configure the model and any known limitations. The models include not only device models, but also bus models.

The following table lists some of the manuals.

Table 2. TEMU Model Manuals

| Document                          | Note                                   |

|-----------------------------------|----------------------------------------|

| Modelling Guide                   | How to write device models             |

| GPIO Bus Model Manual             | Manual for the built in GPIO bus model |

| UART Model Manual                 | Manual for the built in UART bus model |

| AMBA Bus Model Manual             | Manual for the built in AMBA bus model |

| MEC Device Model Manual           | Manual for the ERC32 memory controller |

| LEON2 Device Model Manual         | Manual for the LEON2 on-chip devices   |

| GRLIB GpTimer Device Model Manual | GRLIB manual                           |

| GRLIB IrqMp Device Model Manual   | GRLIB manual                           |

| GRLIB AhbCtrl Device Model Manual | GRLIB manual                           |

| GRLIB ApbCtrl Device Model Manual | GRLIB manual                           |

#### PUBLIC

TEMU: User Manual

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

| Document                          | Note         |

|-----------------------------------|--------------|

| GRLIB AhbUart Device Model Manual | GRLIB manual |

| GRLIB FtmCtrl Device Model Manual | GRLIB manual |

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

# **Chapter 3. System Requirements**

## **3.1. Linux**

## 3.1.1. Strict Requirements

- x86-64 processor

- GLIBC 2.18 or later

## 3.1.2. Recommended Requirements

- At least two times the amount of RAM that the simulated system will contain.

- Qt5 installation via system package manager.

## 3.1.3. Supported Distributions

The following Linux distributions are known to work with TEMU. They are seen as officially supported.

- RHEL 8

- Rocky Linux 8

- Debian 10

- Debian 11

- SLES 12

- SLES 15

Other distributions may work, but are currently not tested on regular basis.

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

Others

# **Chapter 4. Getting Started**

## 4.1. Installation

To install TEMU, the best approach is to use the RPM or DEB files. The latest versions can be downloaded from https://temu.terma.com/.

The following table illustrates which packages should be used on which operating system. Normally generic packages are available. For some older systems specific packages may be available.

OS Package Type

CentOS .rpm

Debian .deb

RedHat Enterprise Linux (RHEL) .rpm

SUSE Linux for Enterprises (SLES) .rpm

Ubuntu .deb

Table 3. Installation Package Suggestions

The following commands can be used to install the different types of packages (where x.y.z is the version number):

.tar.bz2

```

# Install RPM

$ rpm -ivh temu-x.y.z-x86_64-Linux.rpm

# Install DEB

$ dpkg -i temu-x.y.z-x86_64-Linux.deb

# Install Tarball (.tar.bz2)

$ bunzip2 temu-x.y.z-x86_64-Linux.tar.bz2

$ tar xvf temu-x.y.z-x86_64-Linux.tar

```

By default, the packages install TEMU in /opt/temu/3.0.0-pre0. The packages have also been created and bundled with all the normal dependencies they need. This include the standard C++ libraries, so there should be no problem to install and run the emulator on any Linux system. Note that testing is normally done on stable Debian (currently Jessie/8.0), RHEL7 and SLES11.

TEMU consist of a set of libraries and a command line tool. The libraries are normally installed in /opt/temu/3.0.0-pre0/lib and the tools in /opt/temu/3.0.0-pre0/bin/. The binaries and libraries have been liked with the RPATH option, so there is no need to set LD\_LIBRARY\_PATH.

There are also packages for a build which has asserts enabled. Asserts have a performance penalty, which at times can be heavy. Therefore, assert builds are opt-in. These packages installs under:

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

/opt/temu/3.0.0-pre0+asserts/

## 4.2. License Files

See <a href="https://temu.terma.com/">https://temu.terma.com/</a> for more information on licenses. Note that you must have a valid license to run TEMU.

## 4.2.1. Installing a License

A TEMU license is installed using the temu command line tool:

```

$ temu --install-license my-license-file.json

```

It is possible to install multiple license files for the same user (e.g. to enable multiple machines).

## 4.2.2. Revoking a License

To revoke a license in case of e.g. hardware migration, you should issue the revoke command on a license. To get the license ID, use the --list-licenses option to TEMU:

Above you can see two licenses, one which does not match the current computer (hardware address error). To revoke a license for the current computer you should revoke a valid license. Typically, invalid licenses will be either marked as hardware address error or expired for time bounded licenses.

Next step is to revoke the license using the relevant license ID as listed above:

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

Are you sure you wish to revoke the license (yes|no)?

Answer yes if you wish to proceed:

```

Revokation key: '123456789abcdef0...:abcdef0123456789...'

Send the key to Terma in order to be credited with one license activation

NOTE: You cannot use revocations as floating licenses, they are intended for hardware migration only.

```

Then copy the key and send it to Terma to be credited with one license activation.

## 4.2.3. Legacy Licenses

Legacy TEMU licenses are still supported.

TEMU will check your computer for a valid license file at start-up.

By default, TEMU will look for a license file in the following locations (in this order):

```

${TEMU_LICENSE_FILE}

./temu-license.json

~/.config/temu/license.json

```

## 4.3. Running the Emulator

To start the command line interface (CLI), simply run: /opt/temu/3.0.0-pre0/bin/temu or /opt/temu/3.0.0-pre0+asserts/bin/temu. The command line interface exists to run the emulator in stand alone mode.

# 4.4. Creating a New Machine

When TEMU is running it will normally display the temu>-prompt. This is the command prompt.

To create a new machine, it is possible to use one of the bundled CPU configurations in <a href="https://opt/temu/3.0.0-pre0/share/temu/sysconfig/">opt/temu/3.0.0-pre0/share/temu/sysconfig/</a>. Common configurations that instantiate different types of systems are available. The command line scripts can be executed using the exec command. This can be done as illustrated in the following examples:

Listing 1. Create a LEON2 System

```

temu> exec leon2.temu

```

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

### Listing 2. Create a Dual Core LEON3 System

temu> exec leon3-dual-core.temu

# 4.5. Loading and Running Software

When a system has been created, it is time to load and run software in the emulator. The example here assumes that the system was created as in the previous example. To load software which may be in ELF or SREC format the load-command can be used.

When running application software directly, as in contrast to have it loaded by boot software. Then the user needs to ensure that the boot software is simulated. This includes initializing the stack and frame pointers. On some systems timer registers must be initialized.

Execution of software in a single core system can be done by the run and step commands. The runcommand runs the software for a given time (either cycles or seconds), while the step-command single steps the software instruction by instruction. The run and step commands can run and step both machines, clocks and CPUs.

Listing 3. Load and Run Software Image

```

temu> load obj=cpu0 file=rtems-hello.elf

info: cpu0 : loading section 1/1 0x40000000 - 0x4001ec20 pa = 0x40000000

temu> set-reg cpu=cpu0 reg="%fp" value=0x407ffff0

temu> set-reg cpu=cpu0 reg="%sp" value=0x407fff00

temu> run obj=cpu0 pc=0x40000000 time=10.0

```

It is assumed that the user have access to application software and / or cross compilers and is familiar with how to use these tools.

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

# **Chapter 5. Support and Maintenance**

TEMU support and maintenance is at present provided at the following location: https://degitlab-ext.terma.com/termade/temu-issues/temu-issues

It is possible to access the GitLab system for filing support tickets if TEMU is under warranty.

The GitLab system can be used to file bug reports, and user support requests.

Normally, TEMU is licensed with one year of support. Subsequent support and maintenance can be acquired by purchasing a maintenance agreement from Terma.

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

# **Chapter 6. Command Line**

The command line interface (CLI) is easy to use and provides built in help for different commands. To start the command line tool do the following (assuming you are running bash).

```

# Set the PATH to include the temu command line application

$ PATH=/opt/temu/bin:$PATH

# Start TEMU

$ temu

no such file: '~/.config/temu/init'

no such file: './temu-init'

temu>

```

As can be seen above, the command line tool complains about two missing files. These are nothing to bother about at the moment. The files are used to automatically run a set of commands when you start the temu tool.

It is possible to get a list of commands by typing help. Help for an individual command (including lists of arguments the command takes) can be produced by typing help CMDNAME.

# **6.1. Command Line Interface Options**

The command line interface support the execution of non-interactive batch sessions via the --run-\* flags. Multiple run flags can be given to have scripts executed in order. On the first error in a script, TEMU will terminate and not proceed with the next script.

#### --run-commands [filename]

Run the TEMU command-script (CLI-script) in the given file in non-interactive mode. You can provide this option multiple times to execute multiple scripts in sequence. When the last script finishes, the emulator will quit.

### --run-command-string [cmd]

Run [cmd] as a single command as if typed in the interactive command line.

#### --run-script [filename]

Run the Python script in the given file in a non-interactive TEMU-session. The option can be provided multiple times, and scripts will be executed in the sequence they are given on the command line.

#### --interactive

Enter interactive mode after processing --run\* flags. Note that any failed scripts will still terminate TEMU before the interactive mode is entered.

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

## --install-license [filename]

Install a license file.

## --revoke-license [license-id]

Revoke an installed license.

#### --list-licenses

List all installed licenses

When running both CLI scripts and Python scripts, the order will be as specified in the arguments to TEMU. It is possible to run a Python script first, followed by a CLI script or the other way around.

It is also possible to specify a list of scripts without the --run-commands/--run-script flags above, in that case the file type is inferred by the file extension, where the extension .temu will be treated as a TEMU script and the .py extension as a Python script. Passing file names this way will also result in a non-interactive session.

# 6.2. Command Syntax

Normally commands are named by a *noun-verb* format (but there are abbreviations as well). Commands take either a set of named arguments, but some (like the help command) also take positional arguments. In the named format, each argument is separated by a space, and defined using key-value pairs as e.g. help command=memory-assemble.

## 6.3. Variables

The command line allows for variables to be set. These can be set using the var-set command. Variables are expanded if they are given as argument values to commands. When used, variables are referenced as \$var or \${var}.

## 6.4. Help Command

Each command is self-documenting, typing help will show a list of available commands. Typing help command=memory-assemble will show the detailed help for the memory-assemble command, including all arguments and their types.

## 6.5. Commands

This section list some of the commands provided in the CLI. A full list can be generated by running the help command.

## 6.5.1. Snapshot Commands

There are two commands for working with snapshots, the save and restore command.

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

## snapshot-restore

This command restores a serialized snapshot from a file. The read file should be a JSON file written by the save command.

## snapshot-save

The save function writes a snapshot in JSON format to disk. Memory content is typically dumped as raw data in a binary blob (in an auxiliary file). The endianness of this blob is for RAM and ROM contents in the standard models is in host order where the unit size is the word size of the target. For the SPARCv8 target on an x86-64 host this means that the data is stored as sequence of little-endian 32-bit words.

## 6.5.2. Memory Commands

### memory-assemble

This command assembles a string into memory.

## memory-disassemble

This command disassembles memory contents. As assemblers are target dependent, the command takes a CPU parameter.

## memory-load

Load executable file (SREC or ELF format). The Command automatically detects the format of the file.

## memory-read

Read memory and write it to the console.

## memory-write

Modify memory content.

#### memory-map

Map object to memory space. The command assigns an object to an address range in the memory space.

## 6.5.3. Object Commands

When dealing with the emulator object system in the CLI, there are a number of commands that are useful. These include the following:

## object-create

Creates an object, the command takes two or three parameters. The class parameter indicates the class of the object to be created, name indicates the object name (this name should be unique) and the third optional parameter args allows you to list a number of arguments formatted as name:value pairs in a comma separated list. The arguments are class specific, consult the class documentation on the allowed arguments. Example object-create class=Leon3 name=cpu0 args="cpuid:0"

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

## object-connect

Connect two objects together. The command connects an object reference property to an interface provided by another object. The command takes two parameters, parameter a is the property formed as objname.propname, parameter b is the interface reference that the property should refer to, this is formed as objname:ifacename. Examples: connect a=cpu0.memAccess b=cpu0:MmuMemAccessIface, connect a=cpu0.memAccessL2 b=mem0:MemAccessIface

## object-info

This command prints the properties in an object.

## object-list

List the names of all objects created with object-create.

## object-prop-write

In order to assign property values using the property read and write mechanism this command provides that functionality. Depending on the model, a write may have side-effects (by invoking a write handler), side-effects are documented in the model manuals.

## 6.5.4. Plugin Commands

There are several commands in the CLI that helps you deal with and to load plugins. All of these commands have the prefix plugin-.

## plugin-append-path

Add path to plugin search paths

## plugin-load

Load a plugin

#### plugin-remove-path

Remove path from plugin search path

### plugin-show-paths

Print the search paths for plugins

## plugin-unload

Unload a plugin

## 6.5.5. Execution Commands

#### run (object-run)

Run the machine or CPU for a given time

## step (object-step)

Step the machine or CPU for a given number of steps

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

## 6.5.6. Other Commands

## script-run

Run python script

## temu-quit

Quit TEMU

## temu-help

Show help

## temu-version

Show version number

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

# **Chapter 7. Libraries**

The principal library is libTEMUSupport.so. Normally, you never need to directly link to any other library. Remaining libraries which implement CPUs and models, are loaded either in the command line interface by using the plugin-load or its alias import, or by int temu\_loadPlugin(const char \*Path) which is defined in temu-c/Support/Objsys.h.

To use the emulator as a library, simply link to <code>libTEMUSupport.so</code> and initialize the library with <code>temu\_initSupportLib()</code>. The function will among other things ensure that there is a valid license file for you machine. In case there is no valid license file available, the function will <code>terminate your application</code>.

```

#include "temu-c/Support/Init.h"

int

main(int argc, const char *argv[argc])

{

temu_initSupportLib(); // Initialise the TEMU library

return 0;

}

```

temu\_initSupportLib() will terminate your application if there is no valid license file on the system.

# 7.1. Deprecation Policy

TEMU versions are numbered as *Major#.Minor#.Patch#*. I.e. *2.0.1* is a bug fix for major version 2, minor version 0.

## 7.1.1. TEMU 2

This policy is in effect starting with TEMU 2.0.0 (and applies to the C-API). The policy will not change unless the major version is incremented.

Patch version increments are for bug fixes and they will be ABI compatible with previous releases of the same major-minor release (you will not need to recompile your models for them to remain functioning).

Minor version increments will remain source level API compatible, but may deprecate functionality and APIs. Deprecated APIs will be marked as such with GCC / Clang deprecation attributes and noted as deprecated in the release notes. Recompilation of user defined models is recommended as ABI may break (e.g. extra functions at the end of interfaces). Minor versions typically add non-invasive features (more models, additional simple API functionality etc).

Major version increments will remove deprecated functions and APIs. Although, models written using the C-API should in general remain compatible, however, no 100-percent-guarantee is made

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

for this. Major versions can add substantial new features.

## 7.1.2. TEMU 3

As of TEMU 3, the new versioning policy is semantic versioning.

## 7.1.3. Clarification on C++ APIs

At present, any public C++ APIs should be seen as unstable and subject to change without notice.

# 7.2. Experimental Application Programming Interfaces

New API functionality is introduced at regular intervals to help the end user of the system. While simple APIs will be introduced directly, more complex functionality is likely to go through an experimental release cycle (sometimes more than one). For example, source debugging support is being worked on at the time of writing. This is expected to first appear in the command line interface, followed by exposing some functionality via APIs, when these APIs are public, they will be marked as experimental with comments in the headers. Experimental means that the API is subject to change in ways that may be source incompatible, even between patch releases (e.g. between 2.0.0 and 2.0.1).

This way, new APIs can be introduced for public review, and be adapted based on user input.

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

# **Chapter 8. Object System**

TEMU provides a light weight object system that all built in models are written in. The object system exist to provide a C API in which it is possible to define classes and create objects that support reflection / introspection. Conceptually this is similar to GOBJECT, but the TEMU object system is more tailored for the needs of an emulator and a lot simpler. There is also some correspondence to SMP2, but the interfaces are plain C which is needed in order to interface to the object system from the emulator core.

The key features of the object system are the following:

- Standardized way for defining classes and models in plain C.

- Ability to introspect models, even though they are written in C or C++.

- · Automatic save and restore of state

- · Access to object properties by name using scripts

- Standard way for defining interfaces (such as serial port interfaces etc)

- Easy to wrap in order to be able to write models in other languages (e.g. Python)

The object system accomplishes this by providing the following:

#### Class

Blueprint for objects, classes are created, registering properties and interfaces. Classes have names starting with a letter or underscore followed by any number of letters, digits and underscores.

## **Object**

An instantiated class. Normally the TEMU object system takes care of instantiation, however externally created objects can also be registered with the object system (in order to have scripts build the object graph with external classes). Objects have names with the same naming rules as classes, except objects support object name separators with the minus character '-'. This is used to ensure objects inside components have unique global names.

#### **Property**

A named data member of a class (i.e. a field or instance variable). A property is accessible by name (e.g. using strings) and will be automatically serialized by the object system if needed. The system supports all basic fixed with integer types (from <stdint.h>), pointer sized integers (i.e. uintptr\_t and intptr\_t), floats, doubles and references to objects and interfaces. Property names start with a letter or underscore, followed by any number of digits, letters or underscores. Property names can be nested using a period '.' as separator.

## **Pseudo Property**

A named data member of a class without directly backing storage. Pseudo properties are accessible by name, and will be automatically serialized by the object system if they have a set and get function associated. Pseudo properties are useful for custom check pointing logic (e.g.

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

writing out raw data to a file) or for using external classes, or non standard layout types in the object system.

#### Interface

A collection of function pointers allowing classes to provide different behavior for a standardized interface. Similar to an interface in Java or an abstract class in C++. In TEMU this is implemented as structs of function pointers that are registered to a class.

#### Port

A property and interface with an inverse relationship. Connecting an interface property in the port to an interface in another object will automatically introduce a back link from the destination object to the original source object. If a port has been added combining property a and interface b in the source object, and property c and interface d in the destination object. Connecting and will introduce conducted by automatically.

When setting up a simulator based on TEMU, the general approach is the following:

- 1. Create all the needed classes (e.g. load plugins)

- 2. Create all objects for the system (e.g. CPUs, ROM, RAM, MMIO models etc)

- 3. Connect objects (build the object graph)

- 4. Load target software in to RAM or ROM

- 5. Run the emulator

It is possible to query a class or object for properties and interfaces at runtime by specifying the property or interface name as a string.

For example there is a CPU interface that is common to all CPU models, this contain procedures for accessing registers. In addition, there is a SPARC interface which provides SPARC specific procedures (e.g. accessing windowed registers).

The most important core interfaces are the following:

- MemAccessIface

- MemoryIface

- CpuIface

An interface can be queried using the temu\_getInterface function. This function takes an object pointer as first argument and the interface name as second. For example, temu\_getInterface(cpu, "MemAccessIface") will return the pointer to the memory access interface structure provided by the CPU object (or NULL if not available). You need to cast the interface pointer to the correct type. The type mappings are provided in the model manuals.

# 8.1. Object Graph and Interface Properties

The objects created in the object system are connected together by linking interface properties to

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

actual interfaces. That is if an object A has an interface property, this interface property can refer to an interface implemented by some other object B. Under the hood this is a pointer pair with an object pointer and an interface pointer, the interface pointer is a pointer to the struct of function pointers implementing the relevant interface.

# 8.2. Object System Functions

This section lists the most important object system functions. The full documentation is in Doxygen based documentation, this is just a quick way to have an overview.

Table 4. TEMU Object System Functions

| Function                 | Description                                   |

|--------------------------|-----------------------------------------------|

| temu_addInterface()      | Add interface to class                        |

| temu_addPort()           | Bind a property / interface pair as a port    |

| temu_addProperty()       | Add property to class                         |

| temu_addPseudoProperty() | Add pseudo property to class                  |

| temu_checkSanity()       | Look for unconnected interface properties     |

| temu_classForName()      | Get a class object by name                    |

| temu_classForObject()    | Get the class object for an object            |

| temu_connect()           | Connect an interface property to an interface |

| temu_createObject()      | Create a new object from an internal class    |

| temu_deserialiseJSON()   | Restore the state of the emulator             |

| temu_disposeObject()     | Delete object                                 |

| temu_getInterface()      | Get interface pointer by name                 |

| temu_getValue()          | Get property without side-effects             |

| temu_loadPlugin()        | Load a TEMU plugin                            |

| temu_nameForObject()     | Get the name for the given object             |

| temu_objectForName()     | Get a named object                            |

| temu_objsysClear()       | Delete all objects and classes                |

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

| Function             | Description                                |

|----------------------|--------------------------------------------|

| temu_readValue()     | Get property by calling the read function  |

| temu_registerClass() | Create a new class                         |

| temu_serialiseJSON() | Save the state of the emulator             |

| temu_setTimeSource() | Set time source for object                 |

| temu_setValue()      | Set property without side-effects          |

| temu_writeValue()    | Set property by calling the write function |

# 8.3. Properties

Properties are registered fields in a class. They are associated with the type and not with the object instance themselves. Properties have names, types and read- and write functions. Properties are saved in snapshots. Properties are associated with an offset in the model type, meaning they have backing storage.

Property names are legal if they start with a letter or underscore followed by any number of letters, digits or underscores. Properties support nesting via dots as well.

# 8.4. Pseudo Properties

Pseudo properties are properties without explicit backing storage, instead they are registered with not only the read and write functions, but also optional set and get functions. Set and get functions serves the same effect as accessing the raw data in a struct, and are used for snapshots. From the user interface point of view, pseudo properties behave the same as normal properties.

## 8.5. Interfaces

Interfaces are structs populated with function pointers. You can query an interface by name for a given object using temu\_getInterface().

Interface names are legal if they start with a letter or underscore followed by any number of letters, digits or underscores.

## **8.6. Ports**

A very common case is where a source model is connected to a destination model, and the destination model must have a back link to the source model often to a different interface. For example, the IRQ interfaces have an upstream variant IrqIface and a downstream variant IrqClientIface. The upstream variant is used to raise interrupts, while the downstream interface have functions to acknowledge interrupts. To avoid the case where the user forgets to insert the backward link, it is possible to pair interface properties and interfaces together using temu\_addPort().

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

When a port has been added to a class, the connect function will automatically insert the back links if connecting a port in a source object a port in the destination object.

In the interrupt controller case, assume that the class A has an interface reference property irqController and an interface IrqIface and class B an interface reference property named irq and an interface IrqClientIface. Then, the user would do the following:

```

temu_addPort(A, "irqController", "IrqIface", "downstream IRQ port");

temu_addPort(B, "irq", "IrqClientIface", "upstream IRQ port");

// Now normally without ports two connects would be needed

//temu_connect(a, "irqController", b, "IrqClientIface");

//temu_connect(b, "irq", a, "IrqIface");

// With ports, only one connect is needed, it will automatically

// add the reverse link. so, we get both of the links on one

// connect:

// a.irqConroller -> b:IrqClientIface

// b.irq -> a:IrqIface

temu_connect(a, "irqController", b, "IrqClientIface");

```

To list available ports in a class use the class-info command.

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

# Chapter 9. Events

The event API is used to provides a common interface for pushing timed events on the event providers. The API is defined in temu-c/Support/Events.h. The API provides functions for posting events on CPU objects, and provides the ability to post in three different time bases (cycles, nanoseconds and seconds), and the ability to decide if events are synchronized on a single CPU or the parent machine object.

When posting events to a CPU, nano-second events are converted to cycles. This means that you will actually not have NS accuracy for the events. The accuracy is a function of the clock frequency. I.e. for a 100 MHz CPU, the accuracy is 10ns, while a 50 MHz CPU has an event posting accuracy of 20ns.

When posting machine synchronized events, the delta time must be at least in the next time quanta. If not, the event will be slipped to the start of the next quanta (and a warning will be printed to the log).

In the case synchronized events are used, the machine scheduler will adjust its quanta length to ensure that CPUs do not execute longer than needed. Note that synchronized events are executed after a CPU has returned to the machine object, potentially executing non-synchronized events before the machine event, even if the strictly speaking have a trigger time after.

In addition to the different types of timed events, it is possible to stack post an event, in which case it will be executed after the current instruction finishes (in case of CPU synchronized events), or after the current time quanta finishes in case of machine synchronized events.

Events are prioritized as follows:

- CPU synchronized stacked events (in LIFO order).

- CPU synchronized timed events

- Machine synchronized stacked events

- Machine synchronized timed events

That means that machine synchronized events will not be executed until all the stacked events and the normal timer events have been executed.

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

## 9.1. Events from Other Threads

Note that it is in general not possible to post events from an other thread than the one controlling the execution of the emulator. To solve this issue, the function temu\_postCallback() is available. This function is thread safe, and posts an event to be executed alongside the rest of the emulator event queue executions.

The event will be called when the emulator thinks it is safe while it is running, which is when the CPU event timer expires (or when the machine quanta expires by other means). Note that a lone CPU will post a null-event to ensure that the event handlers are triggered at regular intervals and not just when model events are executed. For machines, each CPU runs at most a quanta of time, so the check can be done at quanta expiration.

A possible way to use this capability is when you integrate external hardware / models into your simulator. For example, a separate thread can run and wait on a file-descriptor or socket, when data is available, it reads out the data and posts a thread-safe callback function to be called by the main thread at a safe time. The callback can then take the data that was read from the file-descriptor and inject this over a virtual bus model or write it to emulated memory.

Note that in TEMU 2.2, specific APIs for doing file descriptor and timer monitoring has been added. These are available as the temu\_async\*() functions in the temu-c/Support/Events.h-header.

## 9.2. Notifications

A special type of event is an event that does not have a triggering time. They are instead triggered due to some action or event detected due to other logic inside the emulator. These events are posted using a pub-sub mechanism, with strings as the event key. A model or any other user code can listen for an event which is requested with a specific name. Note that when an event is published, it is assigned an integer ID which is used for fast notifications.

The functions for posting and listening to notifications include:

- temu\_publishNotification()

- temu\_subscribeNotification()

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

- temu\_unsubscribeNotification()

- temu\_notify()

- temu\_notifyFast()

In order to avoid event namespace collisions, all events issued in TEMU are prefixed with temu. or temu:: (the latter is the new style). It is recommended that user published events use their own namespace.

The notification ID 0 is a special notification that is used for indicating "no event", this way it is easy to disable event emission and have the no-event base case be processed cheaply with a single compare and no function call needed.

The temu\_notifyFast-function is an inline function that allows the compiler to get rid of the function call in case the notification id is the null notification.

Current events include (but this is by no means an exhaustive list):

#### temu.cpuErrorMode

CPU entered error mode (halted)

### temu.cpuTrapEntry

CPU trap taken

#### temu.cpuTrapExit

CPU trap handler returned (for targets supporting this, e.g. rett instruction on SPARC)

## temu.breakpoint

Breakpoint hit

### temu.watchpointRead

Watchpoint read access

#### temu.watchpointWrite

Watchpoint write access

#### temu.mil1553Send

MIL1553 message sent, reported by bus object

#### temu.mil1553Stat

MIL1553 status report, reported by bus object

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

# **Chapter 10. Processor Emulation**

The processor emulation capability in TEMU is based on an instruction level simulation engine powered by LLVM. At present the processor emulation is interpreted, but does reach hundreds of MIPS (Millions of emulated Instructions Per wall-clock Second) on modern hardware.

The processor models provide static instruction timing which is useful in order to predict performance in certain cases. Timing does not take pipeline dependencies into account, so there is no simulation of branch prediction, pipeline stalls or superscalar execution. It is possible to insert user provided cache models in the memory space object such models can add more timing accuracy to the emulation at the expense of performance.

A processor object can be embedded inside a machine object. The machine objects can be used in order to control multiple processors as a group. This is the primary way that multi-core, and multi-computer systems are supported.

When running a machine with multiple processors, the processors are temporally decoupled, and the machine synchronizes the processors at various time points. These time points include a mandatory time-quanta, and synchronized events.

# 10.1. Running a CPU or Machine

For a simulator it is important to understand the flow and state transitions of a CPU core and when it terminates and the distinction between stepping and running.

## 10.1.1. CPU States

A CPU can be in three different states:

- Nominal

- Idling

- Halted

The nominal state indicates that the CPU is executing instructions.

Idling indicates that the CPU is not executing instructions but is advancing the CPU cycle counter and event queue. Idle mode is exited when IRQs are raised or the CPU is reset. Idle mode normally indicates either an idle loop (unconditional branch to itself) or power-down mode. In both cases, the CPU will simply forward time to the next event (or if no events are pending return from the core).

Halted mode indicates that the CPU is halted as would happen when a critical error is detected, on the SPARC the halted state corresponds to the SPARC error mode. When entering halted state the CPU core will return and the CPU will remain in halted state until it is reset. It is possible to run a halted core to advance time and execute events (e.g. if there are death event handlers or watchdogs that should reset the system).

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

# Page 29 of 74

### 10.1.2. CPU Exits

A CPU can exit (return from its step / run function) due to a number of reasons.

- Normal exit (step or cycle counter reach its target time)

- · Transition to halted mode

- Breakpoint / watchpoint hit

- Early exit (other reason which can be forced by event handlers or others)

## 10.1.3. Stepping

When a CPU is stepping (e.g. calling its step function), it will execute a fixed number of instructions. When a CPU enters idle mode, a step is seen as advancing to the next event. Except for the event advancement in idle mode, a step can be seen as executing a single instruction. Stepping is not normally done in a simulator, but is often done while debugging software. When the core is in error mode, a step will not advance time however.

When a machine is stepping, it is not the machine that is stepping, but *one* of its CPUs, thus the step command takes an optional parameter cpuidx which can be set when one do not wish to step the default CPU which is the current CPU. As the "current" CPU can change (e.g. when the CPU finishes its scheduling quanta), it is advisable to set this parameter.

## 10.1.4. Running

When a CPU is running, it is set to run UINT64\_MAX steps, and a special end-run-event is posted at the target cycle time. When this end-run event is triggered, the core will stop executing after any stacked events have finished executing. Running a CPU is done in cycles (or in seconds, which is converted to an exact number of cycles).

When machines are run, the CPUs part of the machine will all advance for the time given to the machine. In this case, it is not possible to specify time in the unit "cycles" as each CPU in a machine may have a different clock frequency. Instead, the machine is executed for a given number of nanoseconds.

#### 10.1.5. Instruction Behavior

The emulator is interpreted (at present), in the current release an instruction is executed in the following order:

- 1. Fetch and decode instruction (may call fetch memory access handler)

- 2. Execute instruction semantics (may call memory access handlers, raise traps etc)

- 3. Increment program, step and cycle counters

- 4. Execute any pending events

This means that in an I/O model, if the model wants to terminate with an emergency stop, the step, cycle and program counters will not be updated. To leave

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

the core after this, you need to post a stacked event, which will be executed in step 4. In particular you need to be careful with raiseTrap() and the exitEmuCore() functions defined in the CPU interface. Although, the raiseTrap() function will in general adjust the PC, step and cycle counters and also ensure pending events are executed, the exact results of doing this in a memory handler and an event handler does obviously have different behavior.

If a memory event handler calls <code>enterIdleMode()</code>, this will be entered after the program, step and cycle counters have been incremented. Thus, if you write to a power-down register, then the CPU will continue at the next instruction when returning from the interrupt handler that wakes the CPU. If the power-down system needs to be triggered at the current PC, then you need to use <code>exitEmuCore()</code>.

# 10.2. Event System

A processor is the primary keeper of time in the emulator. The processor keeps track of the progress of time, by maintaining a cycle counter.

Some device models need to be able to post timed events on the CPUs event queue to simulate items such as DMA and bus message timing.

There is a standard API for event posting on CPU models. Timed events are fired at their expiration time, while stack posted events goes on a special event stack. The event will then be triggered after the current instruction has finished executing.

Events are tracked by an event ID which is associated with a function/object pair. Meaning that each object (e.g. an UART instance may have the same function posted as an event), however a single object should not post the same function multiple times while the event is still in-flight. Reposting an event while in flight, will result in a the existing event being descheduled automatically and warning printed in the log.

## 10.3. Multi-Core Emulation and Events

Multi-core processors are simulated by creating a machine object, and adding multiple CPU cores to it, and associating a single memory space object which all the cores (in fact, a non shared memory multi-computer system is a machine object with separate memory spaces for each CPU).

Multi-core processors are temporally decoupled and emulated by scheduling each core for a number of cycles on a single CPU (this window is called a CPU scheduling quanta). This method guarantees full determinism even when emulating multi-core processors. The quanta length can be configured as low as a single nanosecond for the fastest processor, but this has a significant performance impact. The best value need to be experimentally determined for the relevant application, but something corresponding to 10 kCycles is probably a good start. Note that too long quantum means that Inter-Processor Interrupts (IPIs) and spinlocks may have a long response time.

Also, IPIs are typically raised as soon as the destination CPU is scheduled, this is either at the start of the next quanta (i.e. later in time) in case the destination CPU already being scheduled, or at the

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

start of the current quanta (earlier in time) in case the destination CPU has not yet been scheduled.

Set the time quanta to 10 kCycles initially, this is a good starting point. This is also the default value.

The quanta length is set in whole nanoseconds. The quanta property can be set in the machine state object, and it will automatically be converted to cycles based on the individual processor's clock frequency. Thus it is even possible to provide different CPUs with different clock frequencies.

The fact that processors are temporally decoupled does have impact on low level multi-threaded code, such as spin locks and lock free algorithms, where a CPU-core may have to wait excessively long for a spin lock if the owning CPU finishes its quanta before releasing the lock. However, it also ensures that the emulation is deterministic.

IPIs are delivered at the start of either the current quanta or the next depending on whether the destination CPU has already been scheduled.

It is possible to manipulate the machine's time-quanta during execution.

One variant for debugging locking issues is to run with a longer quanta at first and when approaching the locking code, reduce the quanta size to home in on the bug.

As the CPUs usually do not agree on time, the quanta length has an impact on the event system. When posting an event, it normally goes to a single CPU. However, in some cases it is needed to have the different cores agree on time. For these cases, the machine object allows for the posting of synchronized events. These will ensure that the CPU scheduling window is aborted before the quanta is finished and all processor will agree on time (within the granularity of the worst case instruction time).

Synchronized events should always be posted with a firing time in at least the next CPU scheduling quanta. If it isn't the event will be delayed until the next quanta and a warning noted in the log.

## 10.4. CPU Interface

The CPU interface provides a way to run processor cores and to access CPU state such as registers and the program counter.

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

```

void __attribute__((noreturn))

(*exitEmuCore)(void *Cpu, temu_CpuExitReason Reason);

uint64_t

(*getFreq)(void *Cpu);

temu_CpuState (*getState)(void *Cpu);

void

(*setPc)(void *Cpu,

uint64 t Pc);

uint64 t

(*getPc)(void *Cpu);

void

(*setGpr)(void *Cpu,

int Reg,

uint64 t Value);

(*getGpr)(void *Cpu,

uint64_t

unsigned Reg);

void

(*setFpr32)(void *Cpu,

unsigned Reg,

uint32_t Value);

uint32_t

(*getFpr32)(void *Cpu,

unsigned Reg);

void

(*setFpr64)(void *Cpu,

unsigned Reg,

uint64_t Value);

(*getFpr64)(void *Cpu,

uint64 t

unsigned Reg);

uint64_t

(*getSpr)(void *Cpu,

unsigned Reg);

(*getRegId)(void *Cpu,

int

const char *RegName);

(*assemble)(void *Cpu,

uint32 t

const char *AsmStr);

const char*

(*disassemble)(void *Cpu,

uint32 t Instr);

void

(*enableTraps)(void *Cpu);

void

(*disableTraps)(void *Cpu);

void

(*invalidateAtc)(void *Obj,

uint64_t Addr,

uint64_t Pages,

uint32_t Flags);

} temu_CpuIface;

```

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

# **Chapter 11. Memory Emulation**

Memory emulation in TEMU is very flexible, the memory system uses a memory space object to carry out address decoding. The memory space object enables the arbitrary mapping of objects to different address ranges. The emulator will handle the address decoding, which is done very efficiently through a multi-level page table.

# 11.1. Memory Spaces

TEMU provides dynamic memory mapping. Memory mapping is done using the MemorySpace class. A CPU needs one memory space object connected to it. The memory space object does not contain actual memory, but rather it contains a memory map. It is possible to map in objects such as RAM, ROM and device models in a memory space.

The requirement is that the object being mapped implements the MemAccess interface. It can optionally implement the Memory interface as well (in which case the mapped object will support block accesses).

The memory space mapping, currently implements a 36 bit physical memory map (which corresponds to the SPARCv8 architecture definition).

Because it would be inefficient to access through this structure and to build up the memory transaction objects for the memory access interface for every memory access (including fetches), the translations are cached in an Address Translation Cache. The ATC maps virtual to host address for RAM and ROM only. Note that there are six ATCs: one each for read, write and execute operations, and in different variants for user and supervisor privileges.

Memory may have attributes set in some cases (such as for example breakpoints, watchpoints and SEU bits). If memory attributes are set on a page, that page cannot be put into the ATC. Therefore, attribute bits should be set only in exceptional cases.

To map an object in memory, there are two alternatives, one is to use the command line interface command memory-map. The other is to use the function temu\_memoryMap().

# 11.2. Memory Transactions

Memory transactions are passed through the memory space via the temu\_MemAccessIface interface. The memory hierarchy may need to pass along a lot of data for the simulation, so memory transactions are rather large objects that are passed as pointers.

By passing transaction objects around, users always have access to both virtual and physical addresses.

The memory transaction object contains a Value field. The field is 64 bit (8 byte) in size, however the data unit passed in those 64 bits can be either 1, 2, 4 or 8 bytes. The data unit is encoded in the Size field's lower two bits using the log-size of data unit size:

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

0

1-byte transaction

1

2-byte transaction

2

4-byte transaction

3

8-byte transaction

## 11.2.1. Large Transactions

Large transactions are special transactions where more than one data unit is transferred. Devices can opt-in to large transactions by setting the LargeTransactions in its capabilities.

Since data units are at most 8 byte in size, this means that large transactions primarily handle transfers of data blocks of > 8 bytes.

The purpose of these is to for example emulate DMA traffic, (subject to IOMMU handling), send / transfer list loading, etc.

In addition, large transactions can be used to load memories like RAM and ROM with data from the simulation infrastructure.

TEMU 2 only supported single data unit transactions. Large data blocks could be transferred with the MemoryIface, however these were not subject to IOMMU handling. Large transactions is a new feature in TEMU 3. The MemoryIface is now deprecated in favour of large transactions.

In a *normal* transaction, the single data unit is transferred by copying it in the Value field. In a *large* transaction, the Value field is instead expected to contain a pointer to a buffer with the data being transferred.

The buffer can consist of either 1-, 2-, 4- or 8-byte data units.

The type of the buffer is still encoded in the Size field's lower two bits. A transaction is large if the upper 62 bits in the Size field is non-zero.

For large transactions, the Size field contains both the data unit type, and the number of data units that is pointed at in the Value field.

In the following example, the way to create a normal and large transaction is illustrated:

```

void

makeBuffer32(temu_MemTransaction *mt, size_t numWords, uint32_t *data)

{

```

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

```

if (numWords == 1) {

// Create a normal transaction

mt->Value = data[0];

mt->Size = 2;

} else {

// Create a large transaction

// Value contains a pointer to the data

mt->Value = (uintptr_t)(void*)data;

// Data unit size is 4 bytes (use value 2 for encoding)

// Number of words is the number of items going into the upper 62 bit

mt->Size = (numWords << 2) | 2;

}

</pre>

```

Devices do not automatically support large transactions. Devices must opt-in to these using memory access capabilities.

In general, there is no need to support large accesses in a normal device, however if a custom memory is implemented (RAM/ROM/flash/etc), the device should opt-in to handle large transactions.

A large transactions are not subject to automatic endianness swap. Such devices should check the endianness bit in <a href="mt.Flags">mt.Flags</a> with <a href="mt\_HITTLE\_ENDIAN">TEMU\_MT\_LITTLE\_ENDIAN</a> explicitly. This check should only be done for large transactions.

## 11.2.2. Endianness

Endianness support for memory transaction is built by both a device specifying its endianness and the transaction endianness being set in the Flags field.

The following two constants can be used to set the Flags accordingly:

- TEMU MT BIG ENDIAN

- TEMU MT LITTLE ENDIAN

Devices can specify device endianness using the Endianness field in its capabilities. If no endianness is specified (i.e. the capabilities function in the temu\_MemAccessIface is not implemented), the system assumes big endian for the device.

If the memory space detects that a transaction is sent to a device of opposite endianness, the memory space will automatically preform byte swapping for *non-large* transactions.

## 11.2.3. Capabilities

Memory transactions are routed by the memory space to the correct device. However, some device models might emulate little endian devices. Other devices may for example only support word accesses.

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

By implementing the getCapabilities function in the memory access interface, a device can signal to the memory emulation system the endianness, or access sizes supported by the device.

## 11.3. Address Translation Cache

In order to get high performance of the emulation for systems with a paged memory management unit (MMU), the emulator caches virtual to physical to host address translations on a per page level. The lookup in the cache is very fast, but includes a two instruction hash followed by a tag check for every memory access (including instruction fetches).

In the case of an Address Translation Cache (ATC) miss, the emulator will call the memory space object's memory access interface which will forward the access to the relevant device model.

Only RAM and ROM is cached in the ATC, and only if the relevant page does not contain any memory attributes (breakpoints, SEU, MEU etc).

It is possible for models or simulators to purge the ATC in a processor if needed. The means to do this is provided in the CPU interface. Example is given below.

```

// Purge 100 pages in the ATC starting with address 0

Device->Cpu.Iface->invalidateAtc(Device->Cpu.Obj, 0, 100, 0);

```

Note that in normal cases, models do not need to purge the ATC and it can safely be ignored, it is mostly needed by MMU models (that cannot be modelled by the user at present).

# 11.4. Memory Hierarchy and Caches

It is possible to manipulate the memory hierarchy when assembling your machine and connecting the object graph. A cache model can be inserted in the memory space object for more accurate performance modelling. Note that, unless the cache estimates the needed stall cycles on a per page basis, this means that the ATC cannot be used while a cache model is connected. Cache models therefore clears the Page pointer field in the memory transaction object to ensure that the ATC is not used for the memory access.

When the ATC is disabled, the performance of the emulator drops considerably and when a cache model is used that emulates the cache in an accurate manner, it drops even more.

Cache models can be connected to the preTransaction and postTransaction interfaces. Caches should typically only cache RAM and ROM, at present, the user needs to set the TEMU\_MT\_CACHEABLE flag when mapping a device which is cacheable. In principle the MMU should handle this, but at present the SR-MMU does not use the cacheable bits.

Cache models and any other models suitable for handling the pre and post transaction semantics should provide a way to chain an additional model after it. This way, multiple levels of caches and tracing modules can be inserted at will.

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

At present, cacheable objects are only respected as such if they have a size in multiple of page sizes.

To insert a cache model, the typical command sequence is:

A pre-transaction handler will intercept memory transactions before they are executed, it can therefore modify written data. A post-transaction handler will intercept memory transactions after they have been executed, the post transaction handler can therefore modify read data.

Currently, the memory system will look at cache timing from the pre-transaction handlers, but the post transaction handler must be connected to ensure that it can clear the Page pointer in the MemTransaction object.

#### 11.4.1. The Generic Cache Model

The emulator (as of TEMU 2.1) comes bundled with a generic cache model. This model can be used to emulate caches with different number of associativity and line sizes. Most standard cache parameters can be configured in the system. Including the replacement policy (at the moment LRU, LRR and RND are supported), line size, word size, number of sets and number of ways. The generic cache model can also be configured as a split (Harward-architecture) cache, where instructions and data have their own blocks.

Note that when the cache is not split, the parameters (including the tags etc) will be turned into identical values.

The generic cache implements two copies of the cache interface, one for instructions and one for data. These are effectively identical if the caches are not split, so in that case which interface is not relevant.

# 11.4.2. Tracing Memory Accesses

It is possible to utilize the pre- and post-access handlers in the memory space to trace memory accesses. To do so, implement a model exposing the memory transaction interface. In the postAccess handler, the tracing model should clear the page pointer in the transaction object to disable ATC insertion of the memory access. Note that the pre access handler have access to the written value, and the post access handler have access to the read value. While the written value is normally there also in the postAccess handler, it will not be there for atomic exchange operations.

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

# 11.5. Interfaces

### 11.5.1. Memory Access Interface

The memory access interface defines the interface used by objects connected to the emulated memory system. The memory accesses are invoked by a CPU and can be either fetch, read or write operations.

```

typedef struct temu_MemTransaction {

uint64_t Va; // 64 bit virtual for unified 32/64 bit interface.

uint64_t Pa; // 64 bit physical address

uint64_t Value; // Value

uint64_t Size; // Size (see note above)

uint64 t Offset; // Offset in bytes from start of mapping (used for determining

register)

temu_InitiatorType InitiatorType;

temu Object *Initiator; // Initiating object (normally processor, may be null)

void *Page; // Page will be cached in the ATC for this memoy page

uint64_t Cycles; // CPU cycles this memory transaction take

uint32_t Flags; // Flags for use in the memory hierarchy.

void *IR; // Internal pointer

} temu_MemTransaction;

// Exposed to the emulator core by a memory object.

struct temu MemAccessIface {

void (*fetch)(void *Obj, temu_MemTransaction *Mt);

void (*read)(void *Obj, temu_MemTransaction *Mt);

void (*write)(void *Obj, temu_MemTransaction *Mt);

void (*exchange)(void *Obj, temu_MemTransaction *Mt); // Optional

void (*mapped)(void *Obj, uint64_t Pa, uint64_t Len); // Optional, called when

interface is mapped into memoryspace

const temu_MemAccessCapabilities *(*getCapabilities)(void *Obj); // Optional, return

capabilities of device.

};

```

# 11.5.2. Memory Interface

The memory interface is a common interface for memory storage devices. It provides procedures for writing and reading larger blocks of memory. The interface takes an offset from the base address of the object is mapped (normally you use a memory space object to cover the physical address space).

The Size parameter is in bytes, and the Swap parameter specify the log-size in bytes of the data units to read or write. Note that the address/offset is assumed to be aligned at the unit size and the size will be truncated if it does not represent a whole number of data units.

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

I.e. when reading 64 bit words, the size should be 8, 16, 24, ... and the swap argument should be set to 3.

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

# **Chapter 12. Components**

While individual objects are indeed very useful and can be instantiated multiple times connected different ways. The are problematic from a number of reasons.

Many systems consist of many different objects (e.g. an ASIC may have several processors, a couple of I/O models and potentially several additional devices).

Although, while the TEMU command line scripts can be used to construct arbitrary object graphs, it is problematic in the command line as one need to ensure the unique naming of different objects. In the case multiple processors need to be instantiated, several otherwise identical objects need to be created with unique names and attached to the correct CPU and / or memory space objects.

To solve this issue, TEMU provides an internal model called "Component". A component is a collection of objects and exported (and potentially renamed) interfaces.

If you are familiar with software components and e.g. the SMP2 simulator standard, this will sound familiar, and indeed. The TEMU components are modelled after such approaches.

While the generic Component class is useful to construct objects with a unique namespace, the real power comes in the component sub-classes. These sub-classes provide custom constructors and destructors that allow them to create a whole system when they are instantiated.

For example, the SPARCv8 target is bundled with the following components:

- erc32-component

- at 697f-component

- ut699-component

- ut700-component

- ngmp-component

While these can be constructed manually (there are example scripts for this in the sysconfig directory), they are easier to instantiate using the components.

# Chapter 13. Snapshots

As constructing the object graph can be quite complex, it is useful to do this once using the command line interface. The object graph can then be serialized to a JSON file. This is done using the snapshot-save and snapshot-restore commands (these have aliases save and restore).

A snapshot normally consist of the JSON file containing the object graph and property values, and separate binary blobs containing ROM and RAM contents.

The JSON snapshots are human readable, so, simple editing can be done on them by hand using a text editor.

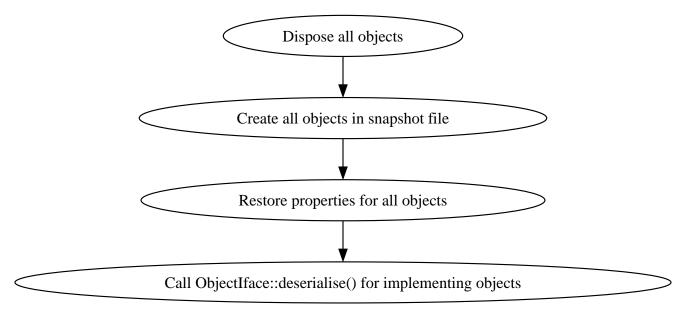

# 13.1. Snapshot Restore Phases

The JSON snapshot mechanism follows a phased approach. This is important in case of implementing custom snapshot restore logic.

Figure 2. Snapshot Restore Phases

In particular this mean that the following holds:

- All non-registered pointers to TEMU objects will become invalid after objects have been recreated.

- Object constructors will be called without arguments. It is up to the model implementor to ensure that restore is successful using properties and custom restore logic.

- Processor and clock custom logic is responsible to restore the event queues. Do not register events outside the object constructor.

# 13.2. JSON Caveats

#### 13.2.1. 64-Bit Values

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

JSON does not allow for larger than 53 bit integers to be stored in a portable way (as JavaScript uses doubles for storing integer values). In case a JSON file is edited, pay attention that when data of type wint64\_t is serialized, it is split into two separate 32 bit values, thus the arrays storing the values will contain twice the elements that are actually in the object's property.

#### 13.2.2. ROM and RAM Contents

Another issue is that JSON is not practical for storing RAM and ROM dumps which are needed if saving and restoring a snapshot not at time 0. Thus ROM and RAM is stored in a binary dump (which is host endian dependent) and the JSON file with the saved system configuration contain references to these RAM and ROM dump files.

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM Rev. no: 3.0-pre

# **Chapter 14. Software Debugging**

There are two supported ways for debugging software with TEMU. Firstly the TEMU CLI supports assembler level debugging in itself. Secondly, TEMU is bundled with a GDB server, this server lets you start up a stand alone program (or run it from the CLI directly).

# 14.1. CLI Based Software Debugging

The TEMU command line interface will when reading ELF files, also load the symbol tables (there is also an API for inspecting ELF symbol tables). Thus, it is possible to disassemble named functions.

When disassembling code based on a function name or a virtual address, the disassembler prints special tokens indicating interesting addresses, such as the PC, nPC (for relevant targets) and trap table pointers. Only one token is printed, and the program counters will always have precedence over other tokens. These tokens are not printed when disassembling using physical addresses.

In addition to disassembling, it is possible to assemble instructions, and modify and inspect both registers and memory.

A global function can be disassembled using the func=name parameter, just give the name of the function to disassemble.

```

temu> dis cpu=cpu0 func=main

( pc) 40001934 040001934 9de3bf98 save %sp, 8088, %sp

(npc) 40001938 040001938 f027a044 st %i0, [%fp + 68]

4000193c 04000193c f227a048 st %i1, [%fp + 72]

40001940 040001940 c027bff8 st %g0, [%fp + 8184]

40001944 040001944 82102001 or %g0, 1, %g1

40001948 040001948 c227bffc st %g1, [%fp + 8188]

4000194c 04000194c 82102000 or %g0, 0, %g1

40001950 040001950 b0100001 or %g0, %g1, %i0

40001954 040001954 81e80000 restore %g0, %g0, %g0

40001958 040001958 81c3e008 jmpl %o7 + 8, %g0

4000195c 04000195c 01000000 sethi 0, %g0

```

A local or static function can be disassembled by giving the function name prefixed with the file name and the scope resolution operator.

```

temu> dis cpu=cpu0 func=test.c::bar

40001924 040001924 9de3bfa0 save %sp, 8096, %sp

40001928 040001928 81e80000 restore %g0, %g0, %g0

4000192c 04000192c 81c3e008 jmpl %o7 + 8, %g0

40001930 040001930 010000000 sethi 0, %g0

```

# 14.1.1. Source Level Debugging

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

TEMU comes with built in source level debugging support, which is based on the DWARF debugging standard. This support is currently experimental and supports source listing, and symbolic and line based breakpoints. Since multiple applications with different DWARF data may be loaded at the same time (e.g. a boot loader and application, or multiple software partitions running under a hypervisor), the DWARF support is based around the notion of debugging contexts, which have been introduced in TEMU 2.2. Currently context management is manual and so is switching the active context. It is at present not possible to inspect symbolic data using the DWARF support.

There are at present three primary areas handled by the commands: context management (i.e. loading, unloading and switching the debugging context), source management (i.e. remapping paths due to moved source directories, and listing source code around the current address), break point handling (i.e. set and control break points). In addition to these, there are some DWARF specific commands that exist to support debugging of the source level debugging code.

The following commands exist at the moment, this explains the purpose of the commands:

#### experimental-debug-load-ctxt

Load an ELF file as a new debugging context.

#### experimental-debug-list-contexts

List all loaded debugging contexts.

### experimental-debug-set-context

Set the current debugging context.

#### experimental-debug-dispose-ctxt

Remove debugging context.

#### experimental-debug-list-source

List source lines around the given address. Pass CPU argument to use the CPUs program counter. By default 5 lines is listed before and after.

#### experimental-debug-add-path

Add a path for searching for relatively named source files.

#### experimental-debug-remap-path

Add a remapping prefix. This is used to remap absolute paths to different directories. E.g. /home/foo/ to /home/bar/ will remap from one user dir to another one. This is particularly useful if the target software is built on a machine that is not the one you are debugging on.

#### experimental-debug-break

Add a breakpoint. Either at an address using the addr parameter or a named location using loc. Locations are in the form of LINENUMBER for locations in the current file (identified using the CPU argument). +NUMBER or -NUMBER for relative lines to the current one. FILE:LINENUMBER for explicit lines or FUNCNAME for a named function.

Doc. no: TERMA/SPD/63/TEMU/GENERAL/SUM

Rev. no: 3.0-pre

#### experimental-debug-mute-break

Prevent break point from printing message on a hit.

#### experimental-debug-demute-break